A Synthesis-Aided Compiler for DSP Architectures (WiP Paper)

PubDate: June, 2020

Teams: Facebook Reality Labs, Cornell University, University of Texas at Austin

Writers: Alexa VanHattum, Rachit Nigam, Vincent T. Lee, James Bornholt, Adrian Sampson

PDF: A Synthesis-Aided Compiler for DSP Architectures (WiP Paper)

Abstract

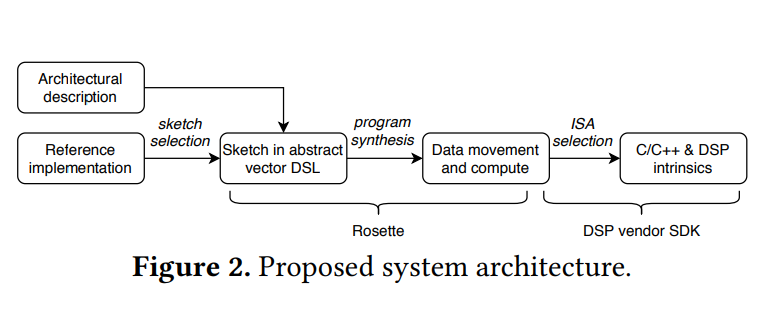

Digital signal processors (DSPs) offer cutting-edge energy efficiency for embedded multimedia computations, but writing high-performance DSP code requires expert tuning. Programmers need to work at a low level of abstraction, manually tailoring vendor-specific instructions to enable vector and VLIW parallelism. Diospyros is a synthesizing compiler that searches for optimal data layouts to enable efficient vectorized code on DSPs. Preliminary results show that for small fixed-size matrix multiply and 2D convolution, Diospyros achieves a 6.4–7.6× speedup compared to vendor-provided optimized kernels, and a 6.5–31.3× speedup over loop-based kernels optimized with the vendor’s included compiler.