FPGA IP for Real-time 4K HDR Image Decoding in VR Devices

PubDate: March 2019

Teams: Tongji University;NARI Group Corporation

Writers: Kamlakannan Kamalavasan; Ratnasegar Natheesan; Kathirgamaraja Pradeep; Sivakumaran Gowthaman; Sivakaneshan Aravint;Ajith Pasqual

PDF: FPGA IP for Real-time 4K HDR Image Decoding in VR Devices

Abstract

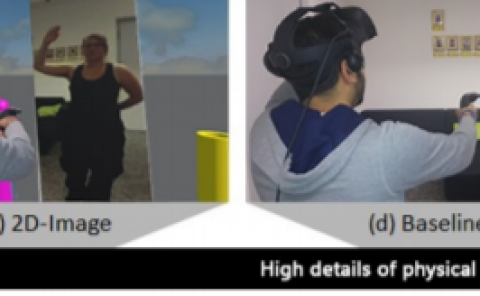

Quad High Definition (QHD/4K) Virtual Reality (VR) Headsets with High Dynamic Range (HDR) technology will provide a superior experience to users. Wireless VR headsets are attractive as it offers freedom on mobility and higher user comfort. Cloud and workstations are capable of rendering 4K HDR scenes in real-time with ease. The efficient transmission of these scenes through wireless network requires the use of compression techniques. Decoding 4K HDR frames at VR devices in real-time is a challenge. Given the power and memory efficiency of the hardware decoders, in this paper we propose JPEG-XT Profile C based hardware architecture to decode 4K HDR frames in real-time. We employ novel methods for merged base and residual layer decoding pipelines, design of probability-based hybrid Huffman lookup table architecture and sparsity aware inverse zig-zag processing. Our decoder is implemented in Xilinx VC707 board and achieved the decoding performance of 4K HDR frames at 30fps while consuming only 7K of LUTs, 12K of Registers and 1980Kb of block memory. Single clocked architecture, use of clock enabling logic and resource sharing in time reduced power consumption to less than 1 watt.